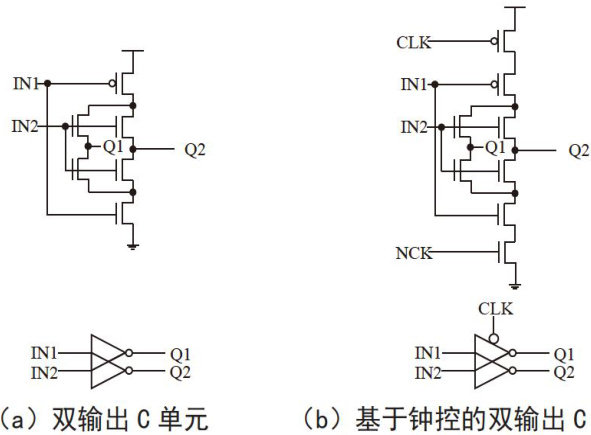

基于双输出C单元的抗三节点翻转锁存器设计

打开文本图片集

中图分类号:TN47;TP332.11 文献标识码:A 文章编号:2096-4706(2026)04-0013-05

Design of a Triple-Node Upset Tolerant Latch Based on Dual-output C-elements

TANG Ye

(School ofComputer ScienceandEnginering,Anhui UniversityofScienceandTechnology,Huainan232oo1,China)

Abstract:With the development ofCMOS technology driving thescaling downof transistor dimensions,radiationinducedTriple-NodeUpset(TNU)inCMOScircuitshavebecomeacriticalissuethreateningthereliabilityofmemorydevices. To mitigate theimpactofsoft erors onintegratedcircuits,thispaperproposes alowoverhead latch designcapableof tolerating Triple-Node Upsets (LCDOCTL).The LCDOCTL latch mainlyconsists of a storage module andaninterception module,and achieves effectiveTNUtolerancebyutilizing inter-celldata feedback.HSPICEsimulationresultsshowthat,incomparison with existing TNU-tolerant latch designs, the proposed LCDOCTL latch achieves an average saving of 5.1% in area, 70.31% in propagation delay, 44.12% in power consumption and 84.66% in Power-Delay Product (PDP).

Keywords:radiation;soft error;latch;TNU; tolerance

0 引言

在深亚微米制造时代,随着晶体管特征尺寸的急剧缩小和电源电压的持续降低,芯片(尤其是数字电路中的存储单元)对辐射引起的软错误愈发敏感。(剩余7022字)